# New Developments in FPGA Devices: SEUs and Fail-Safe Strategies from the NASA Goddard

Melanie Berg, AS&D in support of NASA/GSFC

Melanie.D.Berg@NASA.gov

Kenneth LaBel, NASA/GSFC

Jonathan Pellish, NASA/GSFC

### **Acknowledgements**

- Some of this work has been sponsored by the NASA Electronic Parts and Packaging (NEPP) Program and the Defense Threat Reduction Agency (DTRA).

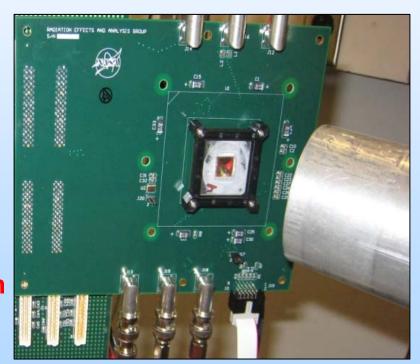

- Thanks is given to the NASA Goddard Radiation Effects and Analysis Group (REAG) for their technical assistance and support. REAG is led by Kenneth LaBel and Jonathan Pellish.

**Contact Information:**

Melanie Berg: NASA Goddard REAG FPGA

Principal Investigator:

Melanie.D.Berg@NASA.GOV

### NASA

#### **Acronyms**

- Application specific integrated circuit (ASIC)

- Block random access memory (BRAM)

- Block Triple Modular Redundancy (BTMR)

- Clock (CLK or CLKB)

- Combinatorial logic (CL)

- Configurable Logic Block (CLB)

- Digital Signal Processing Block (DSP)

- Distributed triple modular redundancy (DTMR)

- Edge-triggered flip-flops (DFFs)

- Equivalence Checking (EC)

- Error detection and correction (EDAC)

- Field programmable gate array (FPGA)

- Finite state machine (FSM)

- Gate Level Netlist (EDF, EDIF, GLN)

- Global triple modular redundancy (GTMR)

- Hardware Description Language (HDL)

- Input output (I/O)

- Linear energy transfer (LET)

- Local triple modular redundancy (LTMR)

- Look up table (LUT)

- NASA Electronic Parts and Packaging (NEPP)

- Operational frequency (fs)

- Power on reset (POR)

- Place and Route (PR)

- Radiation Effects and Analysis Group (REAG)

- Single error correct double error detect (SECDED)

- Single event functional interrupt (SEFI)

- Single event effects (SEEs)

- Single event latch-up (SEL)

- Single event transient (SET)

- Single event upset (SEU)

- Single event upset cross-section (σ<sub>SFII</sub>)

- Static random access memory (SRAM)

- System on a chip (SOC)

#### **Agenda**

- FPGA Devices and Their Tool Environment.

- FPGAs and Critical Applications.

- Single Event Upsets (SEUs) in FPGAs and Fail-Safe Overview.

- Single Event Upsets and FPGA Configuration.

- Single Event Upsets in an FPGA's Functional Data Path and Fail-Safe Strategies.

- Fail-Safe Strategies for FPGA Critical Applications.

- Fail-Safe State Machines.

### FPGA Devices and Their Design Tool Environment

#### **Definitions**

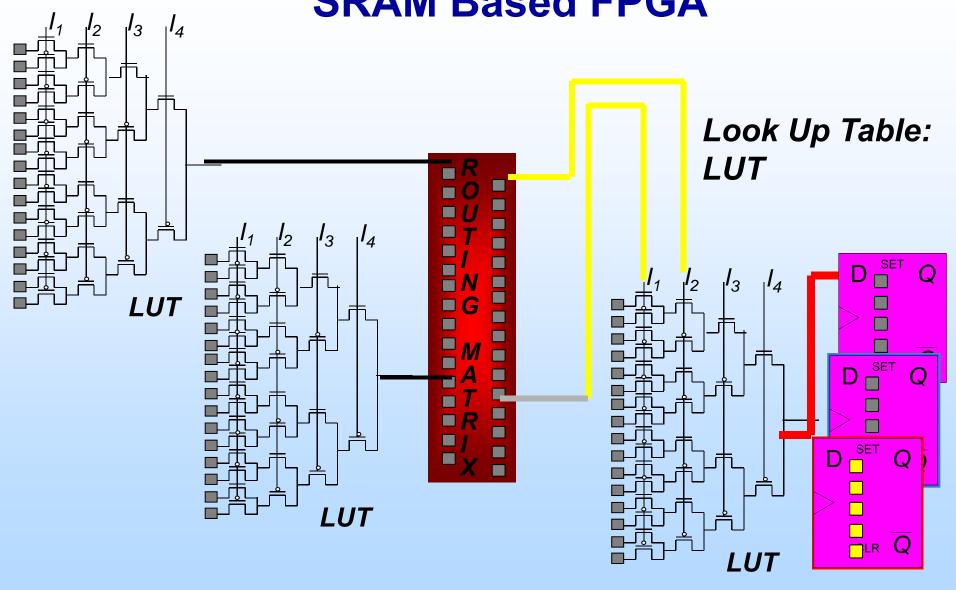

- A Field-Programmable Gate Array (FPGA) is a semiconductor device containing configurable logic components called "logic blocks", and configurable interconnects. Logic blocks can be configured to perform the function of basic logic gates such as AND, and XOR, or more complex combinational functions such as decoders or mathematical functions.

- An application-specific integrated circuit (ASIC) is a semiconductor device designed for a particular use. Its designs are considered more custom. Processors, RAM,

ROM, etc... are examples of ASICs.

An FPGA is an ASIC designed to have a "sea" of configurable logic for general purpose usage.

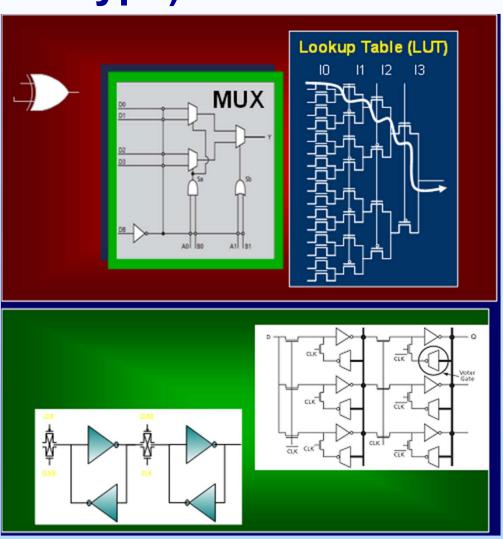

### Creating A Design in An Integrated Circuit Device (FPGA or ASIC)

The objective is to create a hardware design using hardware description language (HDL):

- Clocks,

- Resets,

- Sequential elements (e.g., flip-flops),

- Combinatorial logic.

Combinatorial+Sequential Blocks

- The description gets synthesized into a hardware gate-levelnetlist (GLN: file listing gates and connectivity).

- The synthesized hardware gates are mapped and placed into the cell library (or logic blocks) of the target FPGA or ASIC.

- ASIC flow produces a mask that is handed to a foundry. FPGA flow produces a configuration file.

### **Design Tools**

- Design tools are used for each step of the design process.

- Synthesis: maps HDL into logic blocks (cells) ... outputs gate-level net-lists.

- Place and route (PR): optimizes where the logic blocks and their interconnects should be within the device.

- Synthesis along with PR tools contain optimization algorithms within their tool sets.

- These algorithms are used to optimize area, power, and logic function.

- Tools are difficult to create. Poorly designed tools can create designs that are: functionally incorrect, too large to fit into the target device, or output too much power. Hence, a bad tool can produce unusable designs.

- Equivalence checking (EC) verifies tool output matches HDL.

Best practice is to use a proven vendor's tool set or product might be unreliable or unusable.

**HDL: Hardware description language**

**STA: Static timing analysis**

EC: Equivalence checking

**FPGA User Design Flow**

Functional Specification

Looks like ASIC design flow ... but ...without

but ...without the wait time

Performed by user with manufacturer FPGA specific design tools

**Synthesis**

**HDL**

**Place and Route**

Create Configuration

STA, and back annotated Gate Level Simulation

**Behavioral Simulation**

STA, EC, and Gate

**Level Simulation**

User creates a design that is mapped into a manufacturer provided FPGA

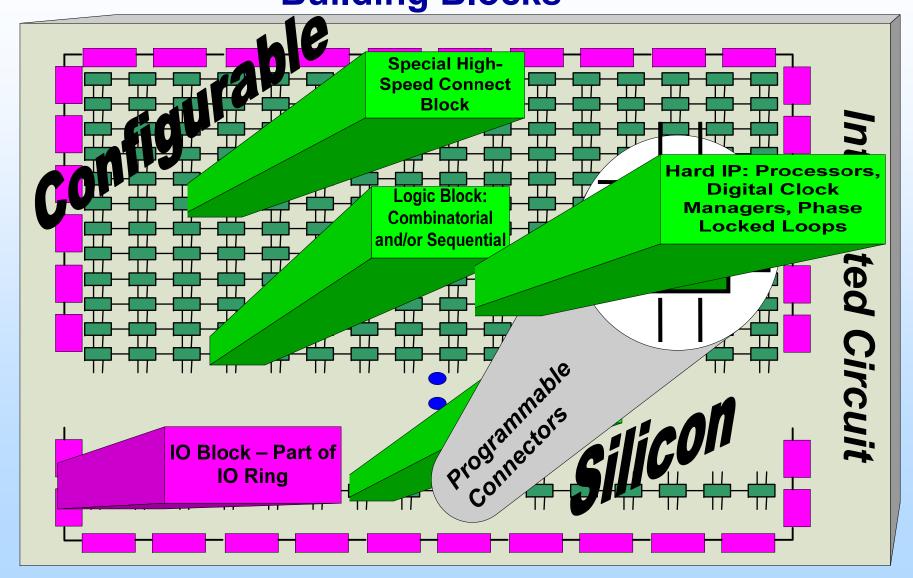

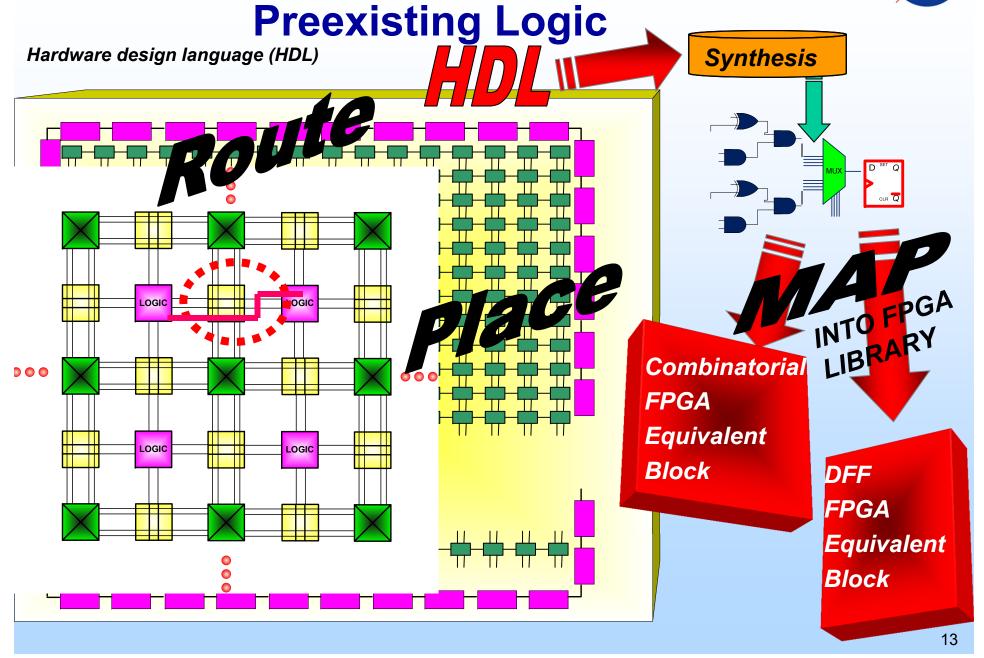

## General FPGA Architecture: Fabric Containing Customizable Preexisting Logic...User Building Blocks

#### **How Do FPGA's Differ?**

- Manufacturer Architecture (not all are listed):

- Configuration,

- User building blocks (combinatorial logic cells, sequential logic cells),

- Routing,

- Clock structures,

- Embedded mitigation, and

- Embedded intellectual property (IP); e.g., memories, complex I/O management, phase locked loops (PLLs), and processors.

- Manufacturer design tool environment:

- Synthesis,

- Place and Route, and

- Configuration management output.

Difference in architectures and tools will affect the final design and design process – users be aware.

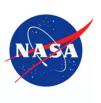

# FPGA Component Libraries: Basic Designer Building Blocks (They Differ per FPGA Type)

- Combinatorial logic (CL) blocks

- Vary in complexity.

- Vary in I/O.

- Sequential logic blocks (DFF)

- Uses global Clocks.

- Uses global Resets.

- May have mitigation.

User Maps the Design Logic into FPGA

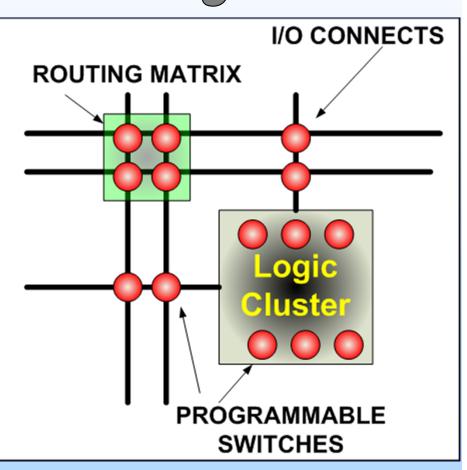

### FPGA Configuration (Storage of User Design Mapping)

Design Mapping)

FPGA MAPPING

- Configuration Defines: Arrangement of pre-existing logic via programmable switches.

- Functionality (logic cluster) and

- Connectivity (routes)

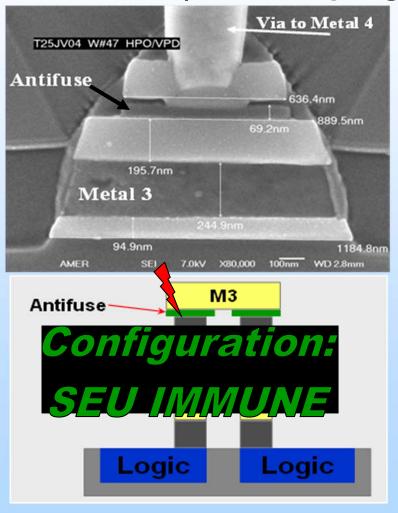

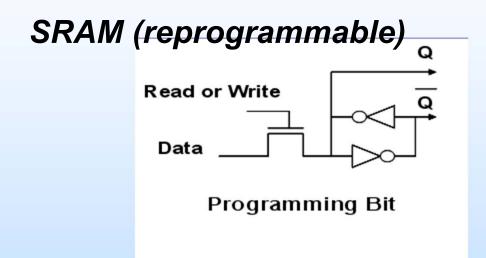

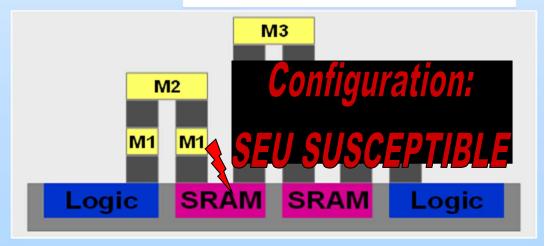

- Programmable Switch Types:

- Antifuse: One time Programmable (OTP),

- SRAM: Reprogrammable (RP), or

- Flash: Reprogrammable (RP).

### FPGA Structure Categorization as Defined by NASA Goddard REAG:

**SEU** cross section:  $\sigma_{SEU}$

- Single Event Upset (SEU)

- Single event functional interrupts (SEFI)

SEFI out of presentation scope

SEU Testing is required in order to characterize the  $\sigma_{SEU}$ s for each of FPGA categories.

### **FPGA's And Critical Applications**

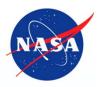

### **Common FPGA Applications**

- Controllers,

- Dataflow and interface adaptation,

- Digital signal processing (DSP),

- Software-defined radio,

- ASIC prototyping,

- Medical imaging,

- Robotic control (vision, movement, speech, etc.,...)

- Cryptology,

- Nuclear plant control,

- The list goes on...

### **Common Applications Example 1:**

**Active Passive**

**New Horizons Pluto and Beyond**

Mars Rover

Spacecube: International Space Station

### Common Applications Example 2: Terrestrial

### Concerns for using FPGA Devices in **Critical Applications**

Critical applications expect to avoid disaster when disaster is probable. humans be damaged or hurt?

Reliability: will the device operate as expected?

Safety: can circuits or

Availability: how often will the system operate as expected?

Recoverability: if the device malfunctions, can the system come back to a working state?

Trust: Will the insertion of the device compromise security?

#### **Sources of FPGA Failures**

Packaging and mounting

Negative bias temperature instability (NBTI)

Hot carrier injection (HCI),

Poor design

choices

Dielectric breakdown (DB)

Total ionizing dose (TID)

Transistor switching stress Electromigration (EM)

> Single event effects (SEEs)

Environmental stress

> Lack of verification

### **How To Protect A System from Failure**

- Investigate failure modes understand risk:

- Reliability testing (temperature, voltage, mechanical, and logic switching stresses).

- Radiation testing: Single event effects (SEE) and total ionizing dose (TID).

- Add redundancy:

- Replication with correction.

- Replication with detection. Requires recovery:

- Switch to another device,

- Try to recover state,

- Start over,

- Alert,

- Do nothing... die.

- Add filtration: e.g., Finite impulse response (FIR) filters or Constant false alarm rate filter (CFAR).

- Add masking: Protect system operation from failures.

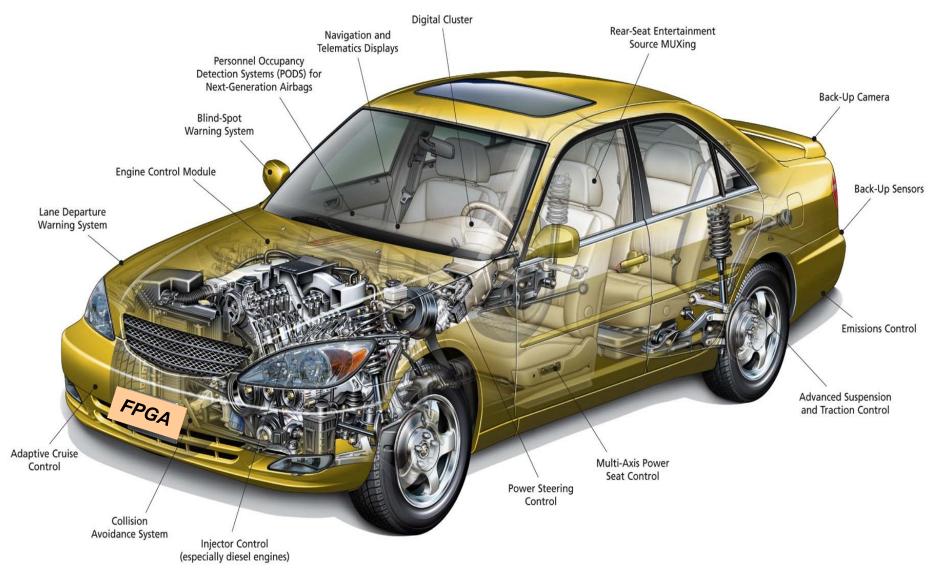

### Single Event Upsets (SEUs) and FPGA NASA Devices

Although there are many sources of FPGA malfunction, this presentation will focus on SEUs as a source of failure.

- Ionizing particles cause upsets (SEUs) in FPGAs.

- Each FPGA type has different SEU error signatures:

- Temporary glitch (transient),

- Change of state (incorrect state machine transitions),

- Global upsets: Loss of clock or unexpected reset,

- Configuration corruption. This includes route breakage (no signal can get through) – can be overwhelming.

- The question is how to avoid system failure and the answer depends on the following:

- The system's requirements and the definition of failure,

- The target FPGA and its surrounding circuitry susceptibility,

- Implemented fail-safe strategies,

- Reliable design practices,

- Radiation environment.

### Characterizing SEUs: Radiation Testing and SEU Cross Sections

SEU Cross Sections ( $\sigma_{sew}$ ) characterize how many upsets will occur based on the number of ionizing particles to which the device is exposed.

$$\sigma_{seu} = \frac{\#errors}{fluence}$$

#### **Terminology:**

Flux: Particles/(sec-cm²)

Fluence: Particles/cm²

$\sigma_{seu}$  is calculated at several LET values (particle spectrum)

Testing with a low flux is imperative with SRAM based devices: this is due to the complexity of the device versus the accelerated rate of exposure.

### SEE Go-no-Go: Single Event Hard Faults and Common Terminology

- Single Event Latch Up (SEL): Device latches in high current state:

- Has been observed in FPGA devices that are currently on the market.

- Some missions choose to use the devices and design around the SEL.

- Single Event Burnout (SEB): Device draws high current and burns out.

- Not observed in FPGA devices that are currently on the market.

- Single Event Gate Rupture: (SEGR): Gate destroyed typically in power MOSFETs.

- Not observed in FPGA devices that are currently on the market.

### Fail-Safe Strategies for FPGA Critical Applications

Goal for critical applications:

Limit the probability of system error propagation and/or provide detection-recovery mechanisms via fail-safe strategies.

### Differentiating Fail-Safe Strategies:

#### Detection:

- Watchdog (state or logic monitoring).

- Simplistic Checking ... Complex Decoding.

- Action (correction or recovery).

#### Masking (does not mean correction):

- Not letting an error propagate to other logic.

- Redundancy + mitigation or detection.

- Turn off faulty path.

#### Correction (error may not be masked):

- Error state (memory) is changed/fixed.

- Need feedback or new data flush cycle.

#### Recovery:

- Bring system to a deterministic state.

- Might include correction.

There is a difference between error masking, correcting, and detecting!

### **Availability versus Correct Operation**

- What is your expected up-time versus down-time (availability)?

- Is correct operation well defined? Needs to be Unambiguous!

- Is system failure well defined? Needs to be Unambiguous!

- Can availability and correct operation be deterministic regardless of error signature?

- Availability:

- Might be defined for general operation.

- Might be only defined during critical operation.

- E.g., device operation during manned missions might be for short periods of time. However, correct operation is mandatory and availability during this window is expected to be %99.9999(999?)

### **Detection and Recovery**

- Not all mitigation schemes require detection.

- Questions/Considerations:

- If your scheme requires detection:

- Can the system detect all error signatures?

- Can the system detect all error signatures fast enough?

- Do different errors require different recovery schemes... can the system accommodate.

- How are you going to verify the detection and recovery?

- How much downtime will there be during recovery Availability is affected by detection and recovery time "Yes or "We know it will work" are not good enough answers: Ask how and if the scheme has been verified!

#### **SEUs and FPGA Variations**

- FPGA susceptibilities (error signatures) vary per FPGA type.

- How does a project manage and protect against FPGA susceptibilities? (mitigation schemes will change based on FPGA type).

- The most efficient solution will be based on understanding:

- SEE theory,

- FPGA SEE susceptibility (per FPGA type),

- Proven mitigation strategies per FPGA type,

- Validation and verification of implemented mitigation strategies, and

- Limitations of tools and/or mitigation schemes.

### Redundancy Is Not Enough

- Just adding redundancy to a system is not enough to assume that the system is well protected.

- Concerns that must be addressed for a critical system expecting redundancy to cure all (or most):

- How is the redundancy implemented?

- What portions of your system are protected? Does the protection comply with the results from radiation testing?

- Is detection of malfunction required to switch to a redundant system or to recover?

- If detection is necessary, how quickly can the detection be performed and responded to?

- Is detection enough?... Does the system require correction?

### Mitigation and FPGA Devices

#### Mitigation can be:

- User inserted: part of the actual design process.

- User must verify mitigation... Complexity is a RISK!!!!!!!!

- Embedded: built into the device library cells.

- User does not verify the mitigation manufacturer does.

- Mitigation should reduce error...

- Generally through redundancy.

- Incorrect implementation can increase error.

- Overly complex mitigation cannot be verified and incurs too high of a risk to implement.

### Radiation Hardened (per SEU) versus Commercial FPGA Devices

- A radiation hardened (per SEU) FPGA is a device that has embedded mitigation.

- Radiation hardened FPGA devices are available to users. They make the design cycle much easier!

- They are considered hardened if:

- Configuration susceptibility is reduced to an acceptable rate.

- Generally, less than one node per 1x10<sup>-8</sup> days.

- Be careful: with millions of nodes, this can translate into 1 or two configuration failures per year.

- However, if the node isn't being used, then your circuit may not be affected by the failure.

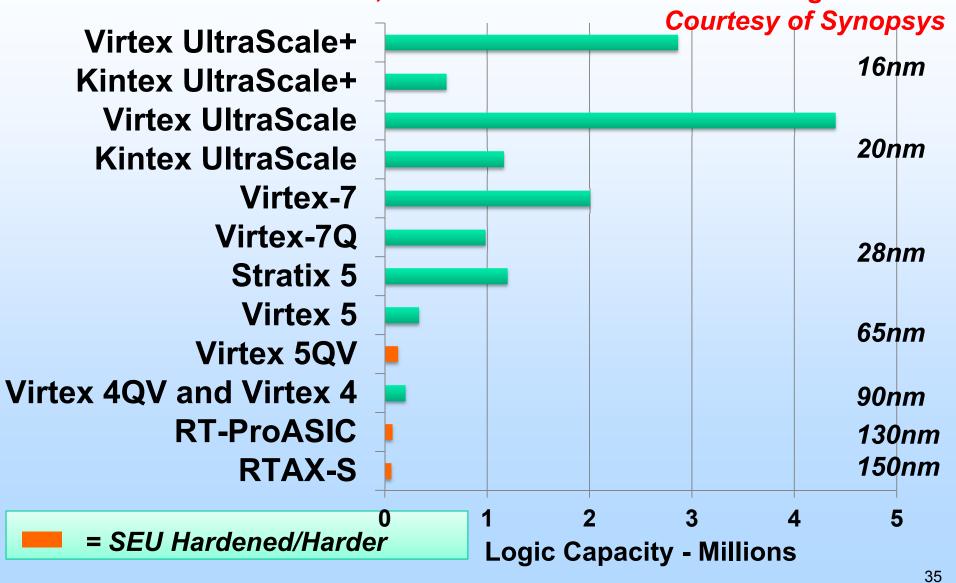

### Radiation Hardened versus Commercial FPGA Device Geometries And Gate Count

As Geometries Get Smaller, More Gates Are Available for Mitigation

## FPGA Devices Listed by Configuration Type (Not All Are Included in The List): Embedded Mitigation

| Manufacturer | Configuration Type | Short List of Device Families | Embedded<br>Mitigation                                              |

|--------------|--------------------|-------------------------------|---------------------------------------------------------------------|

| Altera       | SRAM               | Stratix                       | No                                                                  |

| Microsemi    | Antifuse           | RTAX, RTSXS                   | Clocks +DFFs<br>(configuration is<br>already hardened<br>by nature) |

| Microsemi    | Flash              | ProASIC3                      | Configuration is already hardened by nature.                        |

| Xilinx       | SRAM               | Virtex, Kintex                | No                                                                  |

| Xilinx       | Hardened SRAM      | Virtex V5QV                   | Configuration + DICE DFFs + SET filters                             |

Go to http://radhome.gsfc.nasa.gov, manufacturer websites, and other space agency sites for more information on SEU data and total ionizing dose data.

### FPGA Devices Listed by Configuration Type (Not All Are Included in The List): Susceptibility

| Configuration Type                                        | Short List of Device Families       | Embedded<br>Mitigation                                                 | Most Susceptible Components                                                        |  |

|-----------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| SRAM                                                      | Stratix, Virtex,<br>Kintex          | No                                                                     | Configuration                                                                      |  |

| Antifuse                                                  | RTAX, RTSXS                         | DFFs and clocks<br>(configuration is<br>already hardened by<br>nature) | Combinatorial logic (however susceptibility considered low)                        |  |

| Flash                                                     | ProASIC3                            | Configuration is already hardened by nature.                           | DFFs and clocks                                                                    |  |

|                                                           | Virtex V5QV<br>me.gsfc.nasa.gov, ma |                                                                        | Clocks. In some cases additional mitigation may be necessary for configuration and |  |

| websites, and other space agency sites for more DFFs      |                                     |                                                                        |                                                                                    |  |

| information on SEU data and total ionizing dose data.  37 |                                     |                                                                        |                                                                                    |  |

- Currently, the most common FPGA devices used for NASA driven critical space applications are anti-fuse.

- This is also true for other government agencies.

- However, due to cost of implementation and robustness of design, SRAM-based FPGAs are becoming more popular.

- The usage of SRAM-based FPGA devices introduces a variety of challenges for critical operations because their SEU susceptibility and reduced security.

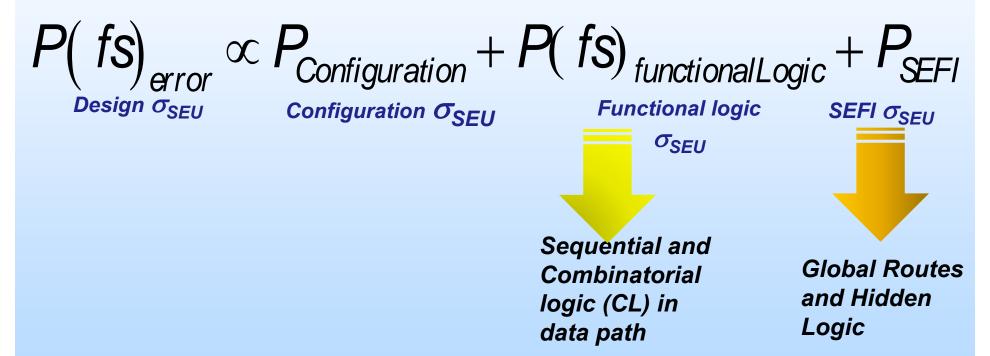

### Preliminary Design Considerations for Mitigation And Trade Space

#### Determine Most Susceptible Components:

$$P(fs)_{error} \propto P_{Configuration} + P(fs)_{functional Logic} + P_{SEFI}$$

- Does the designer need to add mitigation?

- Will there be compromises?

- Performance and speed,

- Power,

- Schedule

- Mitigating the susceptible components?

- Reliability (working and mitigating as expected)?

Impact to speed, power, area, reliability, and schedule are important questions to ask.

### Fail-safe Strategies for Single Event Upsets (SEUs)

- The following slides will demonstrate commonly used mitigation strategies for FPGA devices.

- What you should learn:

- The differences between FPGA mitigation strategies.

- Strengths and weaknesses of various strategies.

- Questions to ask or considerations to make when evaluating mitigation schemes.

- Which mitigation schemes are best for various types of FPGA devices.

- The scope of this presentation will cover fail-safe strategies for configuration and data-path SEUs

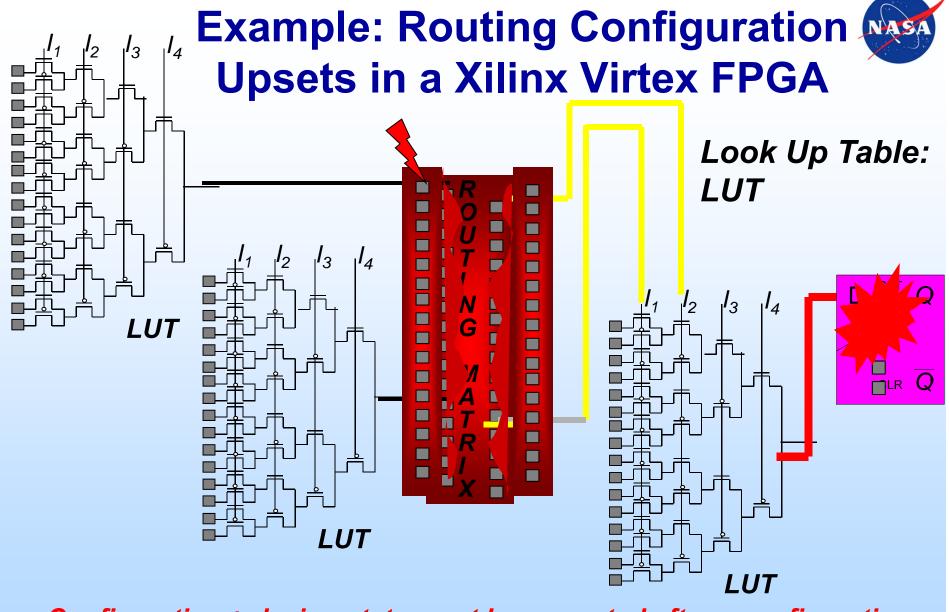

### Single Event Upsets and FPGA Configuration

$P_{configuration} + P(fs)_{functionalLogic} + P_{SEFI}$

### Programmable Switch Implementation and SEU Susceptibility

ANTIFUSE (one time programmable)

### Configuration SEU Test Results and the REAG FPGA SEU Model

$$P(fs)_{error} \propto P_{Configuration} + P(fs)_{functionalLogic} + P_{SEFI}$$

| FPGA<br>Configuration<br>Type | REAG Model                                                                     |

|-------------------------------|--------------------------------------------------------------------------------|

| Antifuse                      | $P(fs)_{error} \propto P(fs)_{functional Logic} + P_{SEFI}$                    |

| SRAM (non-mitigated)          | $P(fs)_{error} \propto P_{Configuration}$                                      |

| Flash                         | $P(fs)_{error} \propto P(fs)_{functionalLogic} + P_{SEFI}$                     |

| Hardened SRAM                 | $P(fs)_{error} \propto P_{Configuration} + P(fs)_{functionalLogic} + P_{SEFI}$ |

#### What Does The Last Slide Mean?

| FPGA<br>Configuration<br>Type | Susceptibility Data-path: Combinatorial Logic (CL) and Flip-flops (DFFs); Global: Clocks and Resets; Configuration                                                                                                                                                                                |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Antifuse                      | Configuration has been designated as hard regarding SEEs. Susceptibilities only exist in the data paths and global routes. However, global routes are hardened and have a low SEU susceptibility.                                                                                                 |  |

| SRAM (non-mitigated)          | Configuration has been designated as the most susceptible portion of circuitry. All other upsets (except for global routes) are too statistically insignificant to take into account. E.g., it is a waste of time to study data path transients, however clock transient studies are significant. |  |

| Flash                         | Configuration has been designated as hard (but NOT immune) regarding SEEs. Susceptibilities also exist in the data paths and global routes (e.g., clocks and resets).                                                                                                                             |  |

| Hardened<br>SRAM              | Configuration has been designated as hardened (but NOT hard) regarding SEEs. Susceptibilities also exist in the data paths and global routes (e.g., clocks and resets).                                                                                                                           |  |

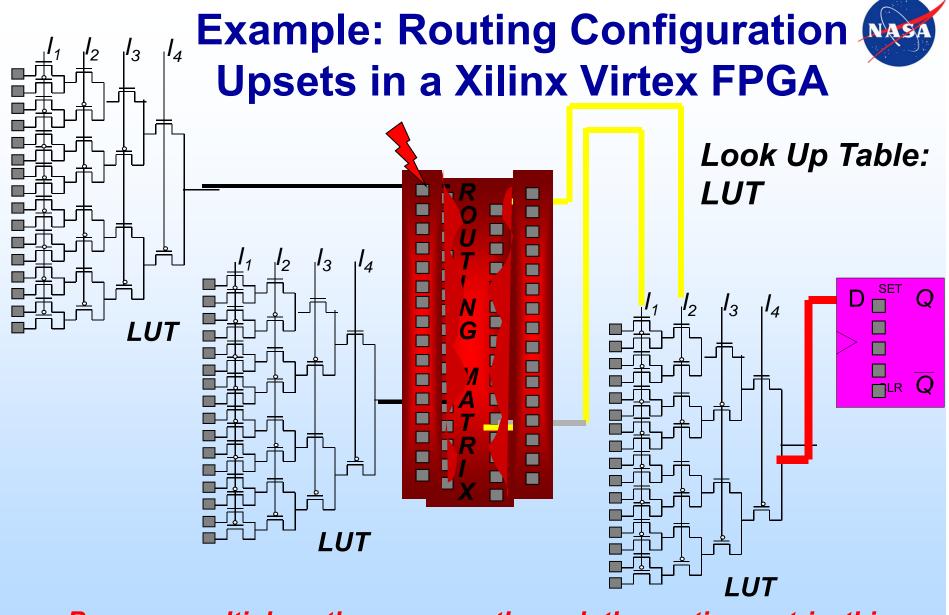

Because multiple paths can pass through the routing matrix, this configuration can be catestrophic – i.e., break simple mitigation

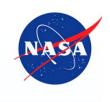

### Traditional SRAM ... One Data Word at a Time

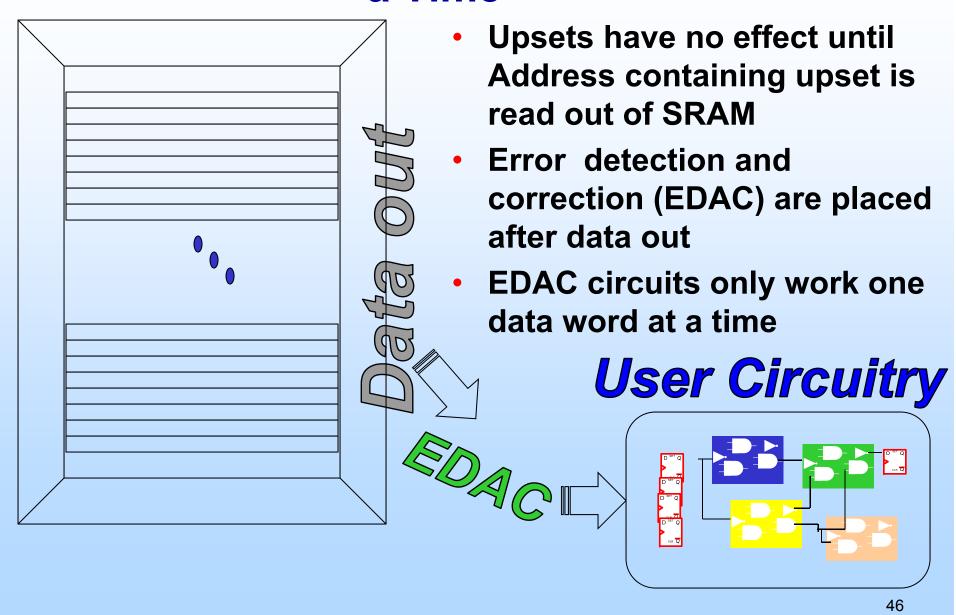

### Configuration SRAM is NOT Utilized the Same Way as Traditional SRAM

We're not dealing with data words anymore. Traditional SRAM EDAC schemes don't quite apply for configuration SRAM

#### Scrubbers: Blind versus Read-back

### NASA

#### **Blind Scrubber**

- Write golden configuration into configuration

- Scrub cycle in the order of ms

- Pros: simple, less area and power, no need for additional non-volatile memory, very fast (great for accelerated testing)

- Cons: Write pointer can get hit during writing and write bad data into configurationhowever, insignificant probability of occurrence (proven in heavy ion SEU testing)

#### Read-back

- Read configuration, calculate correct data; if there is an upset, write corrected data.

- Scrub cycle in the order of s

- Pros, only writes if there is an upset

- Cons, additional non-volatile memory required; slow (only a problem for accelerated testing); takes more area and power; Correction scheme can break (e.g. be limited to detecting and correcting one upset); Consequently, upon an MBU can write bad data to configuration – this has been proven via heavy-ion testing.

### Scrubbers: Internal versus External (1)

- Internal and external scrubbers are used to fix configuration bits:

- Internal scrubber: is created out of hard cores that reside inside the FPGA device; or is created out of user fabric logic blocks located inside the FPGA device.

- External scrubber is implemented in an separate device.

- External scrubbers are usually implemented in anti-fuse FPGA devices.

- Internal scrubbers are obviously more susceptible than external scrubbers.

### Scrubbers: Internal versus External (2)

- Internal scrubbers are usually implemented as readback. Remember read-back scrubbers can break and write bad frames into the configuration due to MBUs.

- Although configuration memory interleaving has been used in the newer SRAM-based FPGAs, a significant number of multiple bit upsets (MBUs) have been observed via Naval Research Laboratory (NRL) laser testing.

- Could be because of laser spot size.

- More testing is expected to be performed early 2016.

## Differentiate Scrubbing for Space Applications and Scrubbing for Radiation Testing Space Application Accelerated SEU Testing

- Only scrub if there is mitigation

- Make scrubber simple to reduce project risk

- Do not scrub constantly not necessary and not good for the system

- Single error correction double error detection (SECDED) scrubbers may not work well due to multiple bit upsets (MBUs)

- Blind scrubbing is the simplest scheme yet readback will also work

- We must scrub!

- Particles cannot overtake the scrubber – i.e., scrubber must be fast enough to stop fast accumulation of configuration SEUs – SCRUB CONSTANTLY

- SECDED scrubbing schemes do not work well during accelerated testing because of MBUs and accumulation

- Generally no time for readback of configuration – hence blind scrubber is the best fit for accelerated testing

#### Warning!

- Fixing a configuration bit does not mean that you have fixed the state in the functional logic path.

- In order to guarantee that the functional logic is in the expected state after the configuration bit is fixed, either the state must be restored or a reset must be issued.

Reliably getting to an expected state after a configuration-bit SEU (that affects the design's functionality) requires one of the following:

- Fix configuration bit + (reset or correct DFFs) or

- Full reconfiguration.

Configuration + design state must be corrected after a configuration SEU hit.

#### Single Event Upsets in an FPGA's Functional **Data Path and Fail-Safe Strategies**

$P_{configuration} + P(fs)_{functionalLogic} + P_{SEFI}$

### Data-path SEUs and Their Affect At The System Level

- A system implemented in an FPGA is a cascade of sequential and combinatorial logic.

- The occurrence of an SET or SEU does not definitively cause system error.

- Probability of a system error due to an SEU depends on many factors:

- Probability of fault generation in a gate (SET or SEU).

- Probability of error propagation will the SET or SEU force the system's next state to be incorrect?

Upsets usually occur between clock cycles: Can cause a system-level malfunction if the SET or SEU will force the system's next state to be incorrect.

- Capacitive filtration: data-path capacitance can stop transient upset propagation; e.g.:

- Routing metal or heavy loading.

- If a transient doesn't reach a sequential element, then it most likely will not cause a system upset.

- Logic masking:

- Redundancy and mitigation of paths can stop upset propagation.

- Turned off paths from gated logic can stop upset propagation.

- Temporal delay: path delays can block temporary SEUs from disturbing next state calculation.

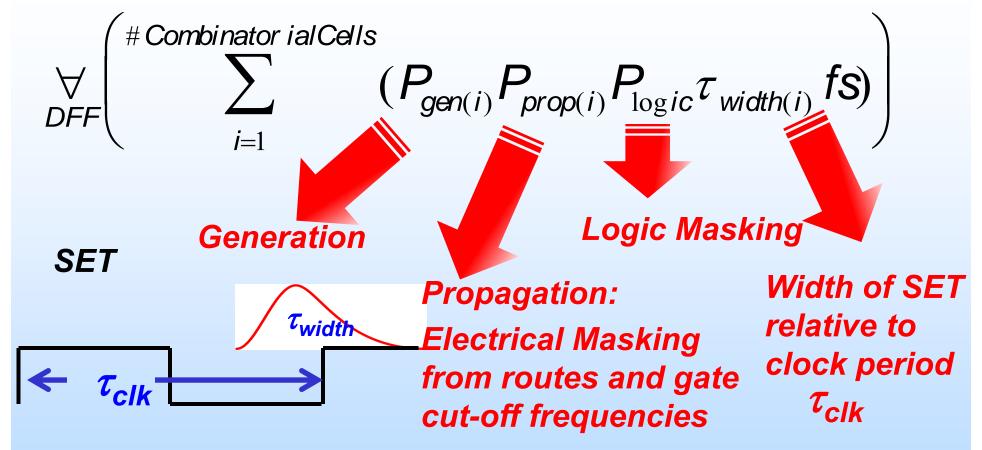

# Data-path SEU Susceptibility and Analysis: the NASA Electronics Parts and Packaging (NEPP) FPGA Model

Berg M.," FPGA SEE Test Guidelines", NASA Radiation Effects and Analysis Group Website:

https://nepp.nasa.gov/files/23779/FPGA\_Radiation\_Test\_Guide lines\_2012.pdf, July 2012.

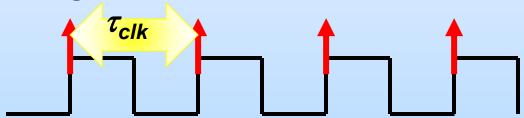

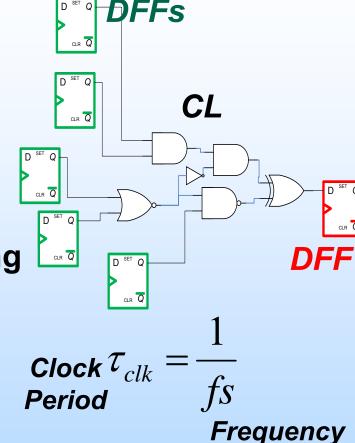

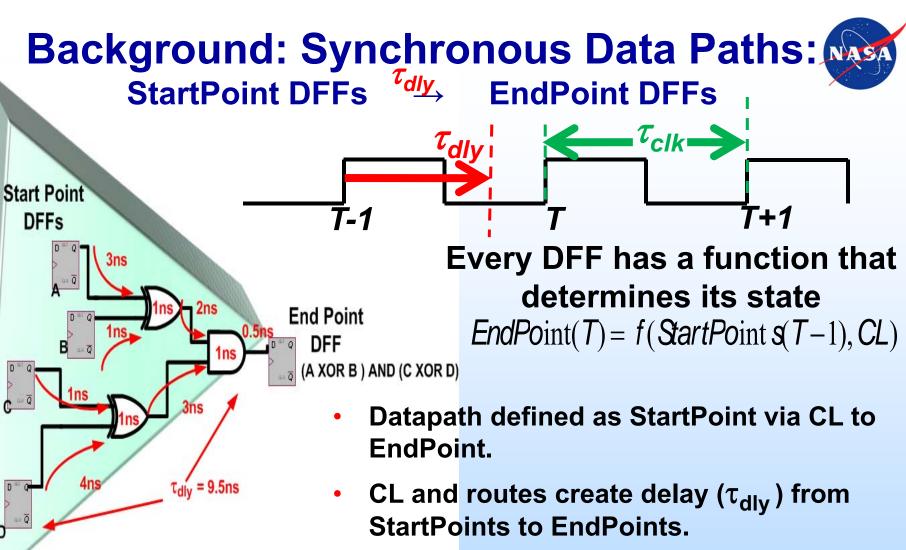

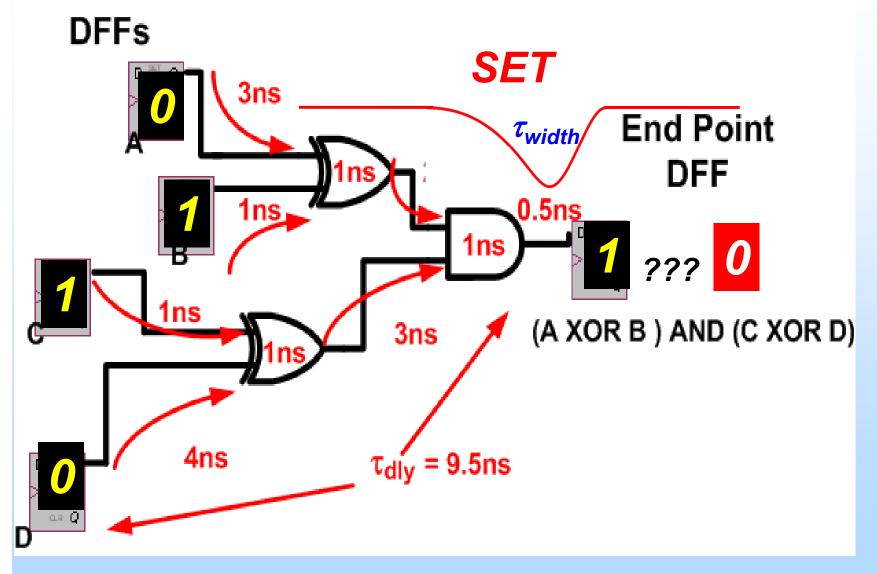

### Background: Synchronous Design Data Path – Sample and Hold

- Synchronous design components:

- Edge Triggered Flip-Flops (DFFs),

- Clocks and resets (global routes),

- Combinatorial Logic (CL).

- All DFFs are connected to a clock.

- DFFs sample their input at the rising edge of clock.

CL compute between clock edges.

Designs are complex – We modularize for simplicity

- Every data path has a unique τ<sub>dlv</sub>.

- τ<sub>dly</sub> is calculated using Static Timing Analysis (STA) design tools.

Modularization: Every DFF has a unique cone of logic

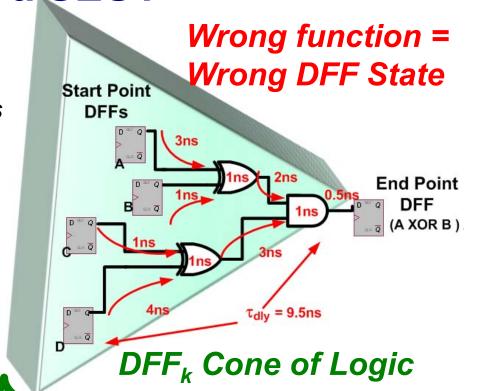

### How can a DFF Contain an Incorrect State from a SEU?

NASA

- DFFs have various modes of reaching a bad state due to SEUs.

- Attribute some modes to EndPoints and some to StartPoints.

We make a clear distinction between DFF SEUs based on Clock state and Capture.

#### EndPoint DFF SEUs + StartPoint DFF SEUs + CL SETs

DFF upsets that occur at the clock edge.

DFF upsets that occur between clock edges and are captured by EndPoints.

Single Event Transients captured by EndPoints.

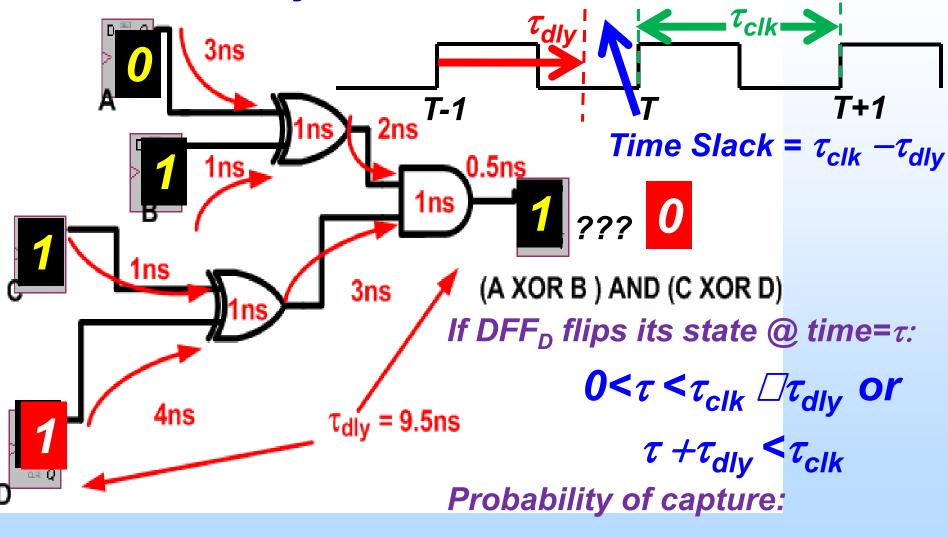

### How Does a StartPoint SEU get Captured by an EndPoint?

$$1 - (\tau_{dly}/\tau_{clk}) = 1 - \tau_{dly} f_S$$

### **Details of Capturing StartPoint DFFs**

$$\forall \left(\sum_{j=1}^{\# StartPoint DFFs} \beta P(fs)_{DFFSEU(j)} (1-\tau_{dly(j)} fs) P_{\log ic(j)}\right)$$

$$Upset \ generated \ internally \ to \ DFF \ between \ clock \ edges$$

$$Design \ Topology \ Design \ Topology \ and \ Topology \ and \ Logic \ Masking$$

- SEU generation occurs in a StartPoint between rising clock edges (βP(fs)<sub>DFFSEU</sub>)

- StartPoint upsets can be logically masked by logic between the StartPoint and its EndPoint

- Design topology and temporal effects:

- Increase path delay (# of gates) decrease probability of capture

- Increase frequency decrease probability of capture

**Synchronous System: CL SET Capture Start Point**

#### **Details of CL SET Capture**

- SET Generation  $(P_{gen})$  occurs between clock edges

- EndPoint DFF captures the SET at a clock edge

- Increase frequency increase probability of capture

- Increase CL increase probability of capture

### NEPP FPGA Model: Putting it All Together

Analyzed Per Particle Linear Energy

Transfer (LET)

$\underbrace{ \begin{array}{c} \textit{EndPoint} \\ \textit{\#EndPoint} \\ \textit{DFFS} \\ \textit{DFFS} \\ \textit{Plogic}(k) \end{array} }^{\textit{\#EndPoint}} \underbrace{ \begin{array}{c} \textit{\#StartPoint DFFS} \\ \textit{StartPoints} \\ \textit{DFFS} \\ \textit{Plogic}(k) \end{array} }^{\textit{\#StartPoint DFFS}} \underbrace{ \begin{array}{c} \textit{StartPoints} \\ \textit{StartPoints} \\ \textit{Plogic}(j) \end{array} }^{\textit{\#StartPoint DFFS}} \\ \underbrace{ \begin{array}{c} \textit{StartPoints} \\ \textit{Plogic}(j) \end{array} }^{\textit{\#CL}} \\ \underbrace{ \begin{array}{c} \textit{\#CL} \\ \textit{DFFSEU}(J) \end{array} (1 - \tau_{aly(j)}fs) ) * P_{logic(j)} ) + \\ \underbrace{ \begin{array}{c} \textit{\#CL} \\ \textit{DFFSEU}(j) \end{array} (1 - \tau_{aly(j)}fs) \end{array} ) * \underbrace{ \begin{array}{c} \textit{Plogic}(j) \\ \textit{Plogic}(j) \end{array} }^{\textit{\#CL}} \\ \underbrace{ \begin{array}{c} \textit{\#CL} \\ \textit{DFFSEU}(j) \end{array} (1 - \tau_{aly(j)}fs) \end{array} }_{i=1} \underbrace{ \begin{array}{c} \textit{Hogic}(i) \\ \textit{Plogic}(i) \end{array} }^{\textit{\#CL}} \\ \underbrace{ \begin{array}{c} \textit{Hogic}(i) \\ \textit{Hogic}(i) \end{array} }^{\textit{Hogic}(i) \end{array} }^{\textit{Hogic}(i) } \\ \underbrace{ \begin{array}{c} \textit{Hogic}(i) \\ \textit{Hogic}(i) \end{array} }^{\textit{Hogic}(i) \end{array} }^{\textit{Hogic}(i) } \\ \underbrace{ \begin{array}{c} \textit{Hogic}(i) \\ \textit{Hogic}(i) \end{array} }^{\textit{Hogic}(i)} \\ \underbrace{ \begin{array}{c} \textit{Hogic}(i) \\ \textit{Hogic}(i) \end{array} }^{\textit{Hogic}(i) } \\ \underbrace{ \begin{array}{c} \textit{Hogic}(i) \\ \textit{Hogic}(i) \end{array} }^{\textit{Hogic}(i) } \\ \underbrace{ \begin{array}{c} \textit{Hogic}(i) \\ \textit{Hogic}(i) \end{array} }^{\textit{Hogic}(i)} \\ \underbrace{ \begin{array}{c} \textit{Hogic}(i) \\ \textit{Hogic}(i) \end{array} }$

StartPoints and CL need to be captured by an EndPoint... hence data path derating factors exist.

Component Contribution to  $\sigma_{SEU}$  across Frequency and Gate Count

|                 | Frequency                     | # of Gates in Path            |

|-----------------|-------------------------------|-------------------------------|

| <b>EndPoint</b> | <b>Directly Proportional</b>  | N/A                           |

| StartPoint      | <b>Inversely Proportional</b> | <b>Inversely Proportional</b> |

| CL              | <b>Directly Proportional</b>  | <b>Directly Proportional</b>  |

|                 |                               | 65                            |

#### **Current Use of NEPP FPGA Model**

Currently, model is used to better understand heavy-ion SEU data:

Great for measuring mitigation scheme strength.

### **Data Path Fail-Safe Strategies**

#### Selecting a Fail-Safe Scheme (1)

- Fail-Safe scheme selection will depend on:

- Requirements,

- FPGA device type, and

- design architecture.

- Everything depends on requirements. Do not overdesign or underdesign.

- How long is the system required to operate?

- How much error can be tolerated?

- What type of errors can be tolerated or untolerated?

- FPGA device type considerations:

- Does the device have embedded mitigation?

- Is the device's configuration soft?

#### Selecting a Fail-Safe Scheme (2)

- Design Architecture considerations:

- Flushable systems:

- Systems that can tolerate next-state≠expected-state.

- However, if next-state≠expected-state, next-state is always deterministic.

- Examples of tolerable system flushing:

- Relatively frequent soft or hard system resets.

- Safe-state machines?????????

- Roll-back systems.

- Non-flushable systems:

- next-state must always equal expected-state during a given window of operation.

- "Must always equal" is an exaggeration: cannot be %100 (no such thing) however, %99.9999 might be feasible.

- Example: while an FPGA is controlling a manned mission during take-off – the operation is not interruptible.

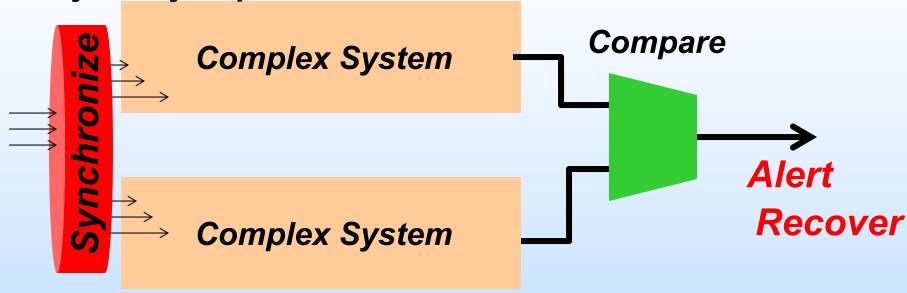

### Dual Redundant Systems (Detection Systems)

#### **Dual Redundancy Example**

Synchronization is not always easy or predictable

- Dual redundant systems cannot correct; they can only detect.

- Form of correction: Roll-back + dual redundancy:

- Roll-back is not a sufficient solution for systems with highly susceptible hardware. Not bad for systems where memory is the most susceptible.

- Roll-back may not satisfy requirements for critical applications (next-state ≠ expected state).

- Alert systems must be highly reliable and verifiable.

# Mitigation – Fail Safe Strategies That Do Not Require Fault Detection but Provide SEU Masking and/or Correction: Triple Modular Redundancy (TMR)

All terminology presented is now used by standard commercial tools:

Mentor Graphics and Synopsys

### **TMR Schemes Use Majority Voting**

$MajorityVoter = I1 \land I2 + I0 \land I2 + I0 \land I1$

| 10 | l1   | <b>I</b> 2 | <b>Majority Voter</b> |

|----|------|------------|-----------------------|

| 0  | 0    | 0          | 0                     |

| 0  | 0    | 1          | 0                     |

| 0  | 1    | 0          | 0                     |

| 0  | 1    | 1          | 1                     |

| 1  | 0    | 0          | 0                     |

| 1  | 0    | 1          | 1                     |

| 1  | 1    | 0          | 1                     |

|    | 2006 | of 3       | 1                     |

Best 2 out of

Triplicate and Vote

#### **Triplicate and Vote**

Singular Data Path

Redundant Data Path

### **TMR** Implementation

- As previously illustrated, TMR can be implemented in a variety of ways.

- The definition of TMR depends on what portion of the circuit is triplicated and where the voters are placed.

- The strongest TMR implementation will triplicate all data-paths and contain separate voters for each datapath.

- However, this can be costly: area, power, and complexity.

- Hence a trade is performed to determine the TMR scheme that requires the least amount of effort and circuitry that will meet project requirements.

- Presentation scope: Block TMR (BTMR), Localized TMR (LTMR), Distributed TMR (DTMR), Global TMR (GTMR).

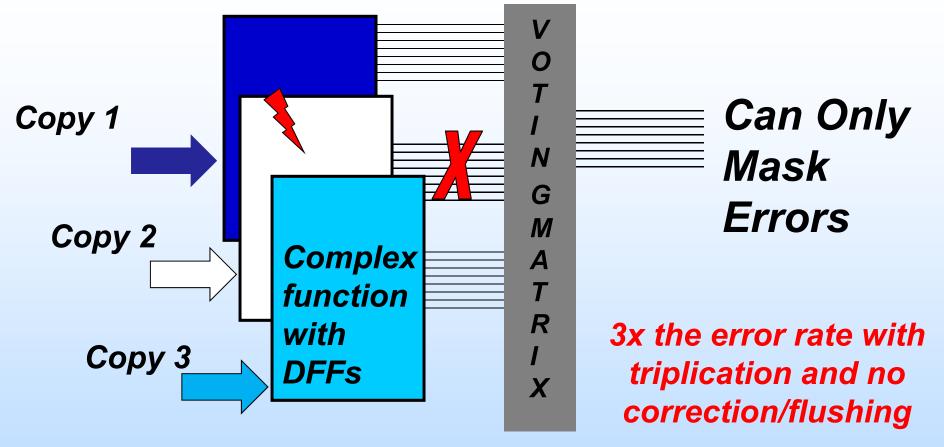

### Block Triple Modular Redundancy: BTMR 👺

- Need Feedback or flushing to Correct

- Cannot apply internal correction from voted outputs

- If blocks are not regularly flushed (e.g. reset), Errors can accumulate – may not be an effective technique

### BTMR Clarification: Very Important Point!!!!

- Adding more blocks with voting on the outputs:

- Only masks upsets.

- Does not correct upsets.

- Will not prolong normal operation!!!!!!!!

However, will mask upsets.

- Device lifetime does not last longer ...if malfunction is expected within one day, then all devices are expected to malfunction within one day. Because there is NO correction.

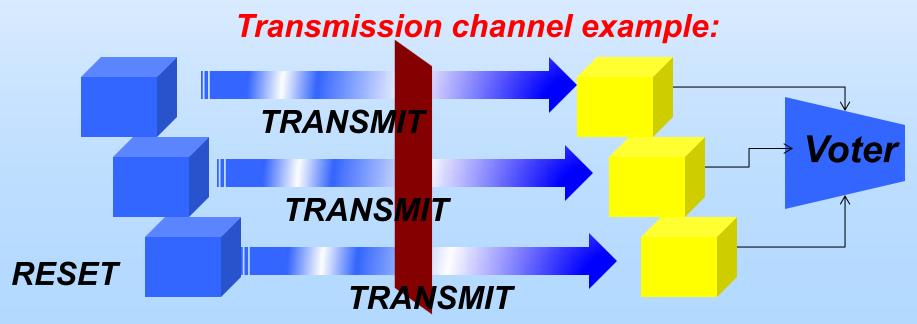

- However, if operation doesn't need to be prolonged – i.e, flushable circuits, then BTMR can be great.

- Shift Registers.

- Transmission channels: It is typical for transmission channels to send and reset after every sent packet.

- Lock-Step microprocessors that have relaxed requirements such that the microprocessors can be reset (or power-cycled) every so-often.

# If The System Is Not Flushable, Then BTMR May Not Provide The Expected Level of Mitigation

- BTMR can work well as a mitigation scheme if the expected MTTF >> expected window of correct operation.

- But... If the expected time to failure for one block is less than the required fullliveliness availability window, then BTMR doesn't buy you anything.

- If not thought out well, BTMR can actually be a detriment – complexity, power, and area, and false sense of performance.

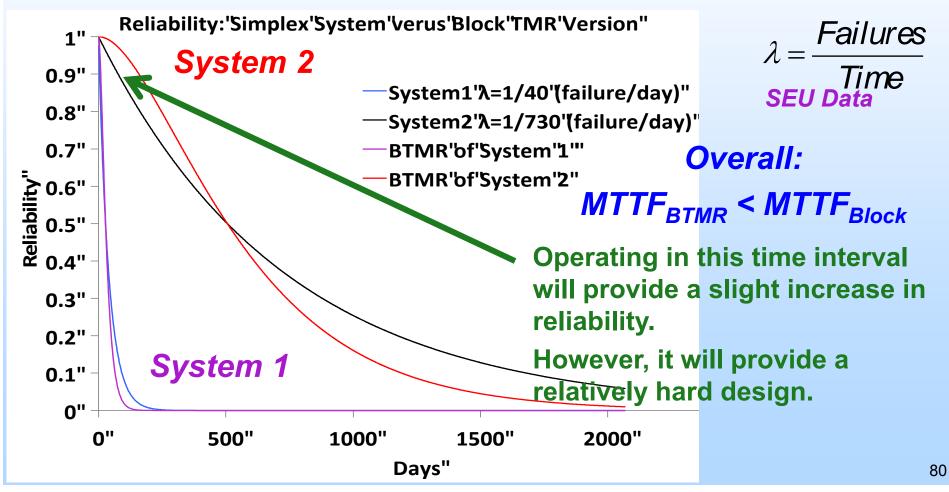

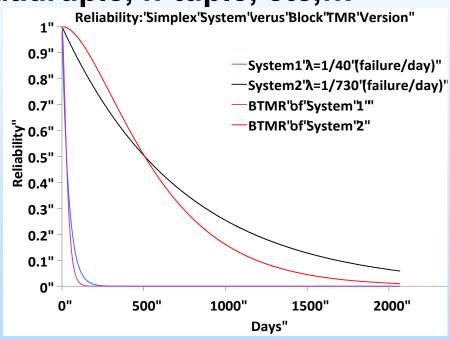

### Explanation of BTMR Strength and Weakness using Classical Reliability Models

| Relibility for 1 block (R <sub>block</sub> ) | Relibility for BTMR (R <sub>BTMR</sub> ) | Mean Time to Failure for 1     | Mean Time to Failure BTMR       |

|----------------------------------------------|------------------------------------------|--------------------------------|---------------------------------|

|                                              |                                          | block (MTTF <sub>block</sub> ) | (MTTF <sub>BTMR</sub> )         |

| e- ht                                        | $3 e^{-2\lambda t} - 2 e^{-3\lambda t}$  | $1/\lambda$                    | $(5/6 \lambda) = 0.833/\lambda$ |

# High Reliability: Full Operation Required for Small Window of Time

- If a small time window of operation is required and reliability is expected to be high, then adding redundancy: Triple, quadruple, n-tuple, etc,... can be used.

- Early in the window, as you add correctly implemented redundancy, the reliability stays high longer.

However!!!!!!! This is not true as time goes on.

This is only true during time near start time (from system flush)

# High Reliability: Full Operation Required for Large Window of Time

If a large time window of operation is required and reliability is expected to be high, then adding redundancy: Triple, quadruple, n-tuple, etc,...

should not be used.

As you add more redundancy, overtime, the reliability will drop very quickly.

Using more redundancy (adding more blocks) will be less reliable over time

### What Should be Done If Availability Needs to be Increased?

- If the blocks within the BTMR have a relatively high upset rate with respect to the availability window, then stronger mitigation must be implemented.

- Bring the voting/correcting inside of the modules... bring the voting to the module DFFs.

The following slides illustrate the various forms of TMR that include voter insertion in the data-path.

| TMR<br>Nomenclature | Description  DFF: Edge triggered flip-flop; CL: Combinatorial Logic | TMR<br>Acronym |

|---------------------|---------------------------------------------------------------------|----------------|

| Local TMR           | DFFs are triplicated                                                | LTMR           |

| Distributed TMR     | DFFs and CL-data-paths are triplicated                              | DTMR           |

| Global TMR          | DFFs, CL-data-paths and global routes are triplicated               | GTMR or XTMR   |

## Describing Mitigation Effectiveness Using A Model

DFF: Edge triggered flip-flop

**CL:** Combinatorial Logic

$$P(fs)_{error} \sim P_{configuration} + P(fs)_{functionalLogic} + P_{SEFI}$$

$$P(fs)_{DFFSEU \rightarrow SEU} + P(fs)_{SET \rightarrow SEU}$$

Probability that an SEU in a DFF will manifest as an error in the next system clock cycle

Probability that an SET in a CL gate will manifest as an error in the next system clock cycle

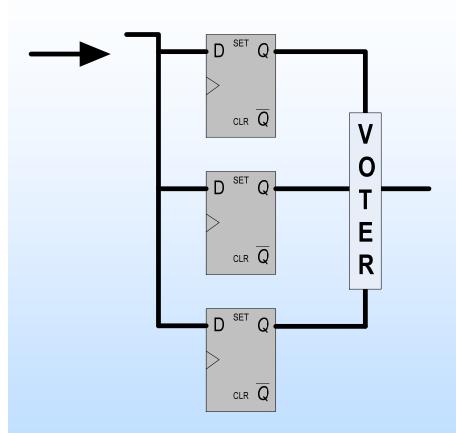

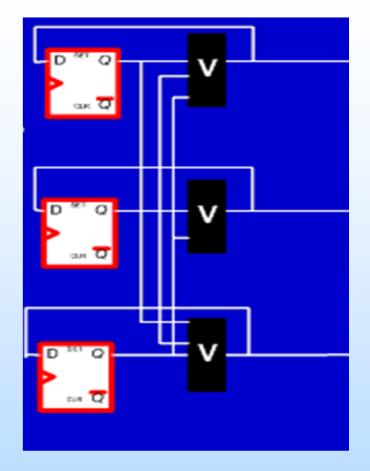

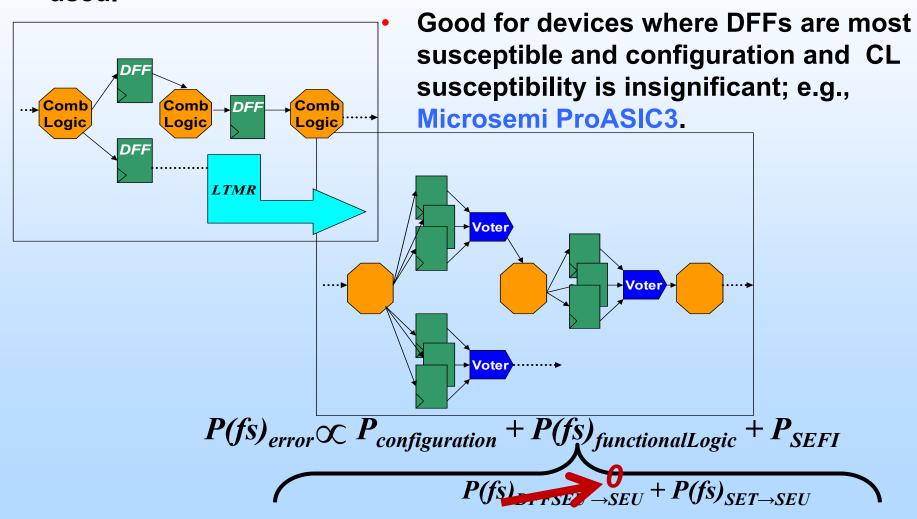

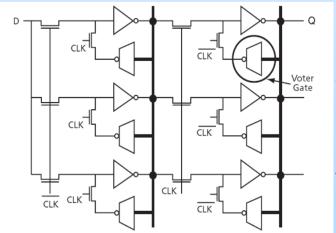

### Local Triple Modular Redundancy (LTMR)

- Only DFFs are triplicated. Data-paths are kept singular.

- LTMR masks upsets from DFFs and corrects DFF upsets if feedback is used.

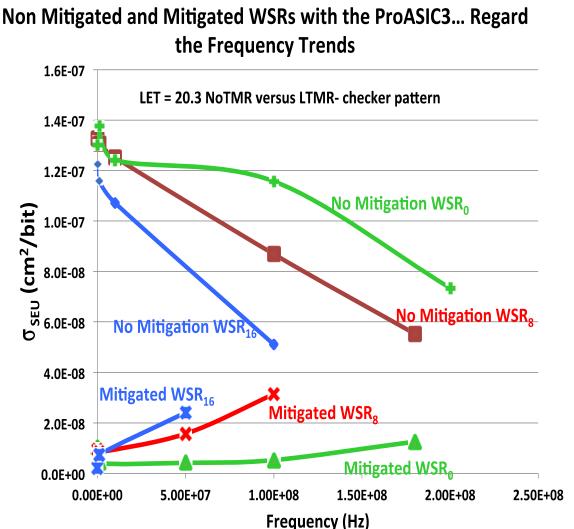

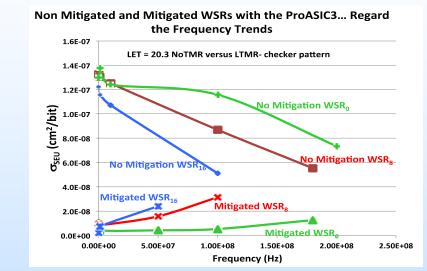

### Adding LTMR to a Microsemi ProASIC3 Device

NASA

LET: Linear Energy Transfer; WSR: windowed shift register

- Microsemi ProASIC3

DFFs are the most susceptible (to heavy-ion SEUs)

data-path components.

- Adding LTMR decreases design sensitivity to SEUs.

### Adding LTMR to a Microsemi ProASIC3 Device versus RTAXs Embedded LTMR

NASA

LET: Linear Energy Transfer; WSR: windowed shift register

- At lower LETs, user inserted LTMR to the ProASIC3 has similar SEU response to Microsemi RTAXs series.

- Higher LETs, clock tree upsets start to dominate and LTMR in the ProASIC3 is not as effective.

- For most critical applications, these cross-sections will produce acceptable upset rates.

Embedded LTMR in a DFF cell RTAXs series.

### LTMR Should Not Be Used in An SRAM Based FPGA

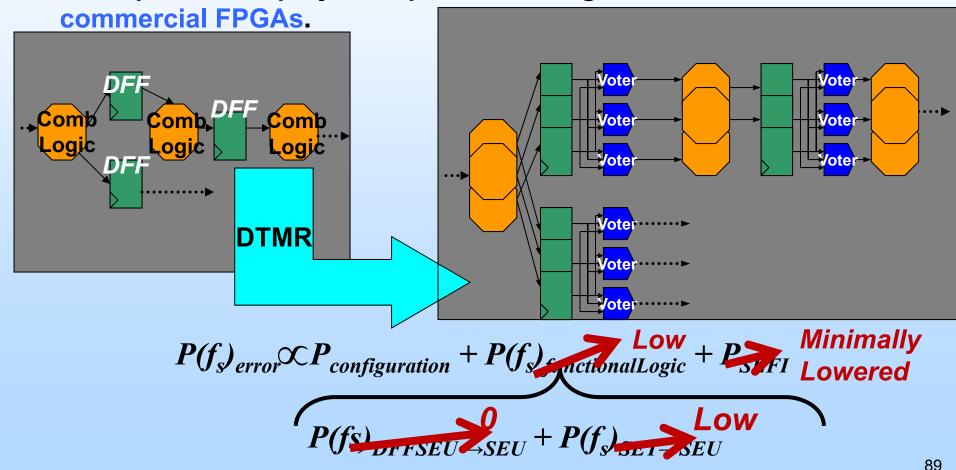

#### Distributed Triple Modular Redundancy (DTMR)

- Triple all data-paths and add voters after DFFs.

- DTMR masks upsets from configuration + DFFs + CL and corrects captured upsets if feedback is used.

- Good for devices where configuration or DFFs + CL are more susceptible than project requirements; e.g., Xilinx and Altera

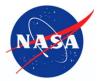

#### Global Triple Modular Redundancy (GTMR)

- Triple all clocks, data-paths and add voters after DFFs.

- GTMR has the same level of protection as DTMR; however, it also protects clock domains.

- Good for devices where configuration or DFFs + CL are more susceptible than project requirements; e.g., Xilinx and Altera

# Theoretically, GTMR Is The Strongest Mitigation Strategy... BUT...

- Triplicating a design and its global routes takes up a lot of power and area.

- Generally performed after synthesis by a tool

part of RTL.

- Skew between clock domains must be minimized such that it is less than the feedback of a voter to its associated DFF:

- Does the FPGA contain enough low skew clock trees? (each clock + its synchronized reset)x3.

- Limit skew of clocks coming into the FPGA.

- Limit skew of clocks from their input pin to their clock tree.

- Difficult to verify.

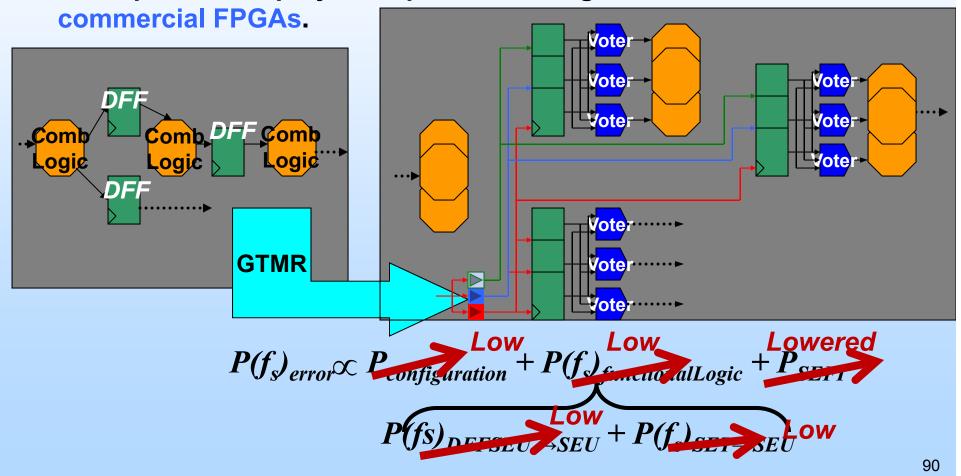

### **Logic Partitioning**

- With BTMR, DTMR, and GTMR the logic needs to partitioned such that their TMR domains do not overlap.

- This can make design implementation in a selected device impossible: area, timing, and place and route.

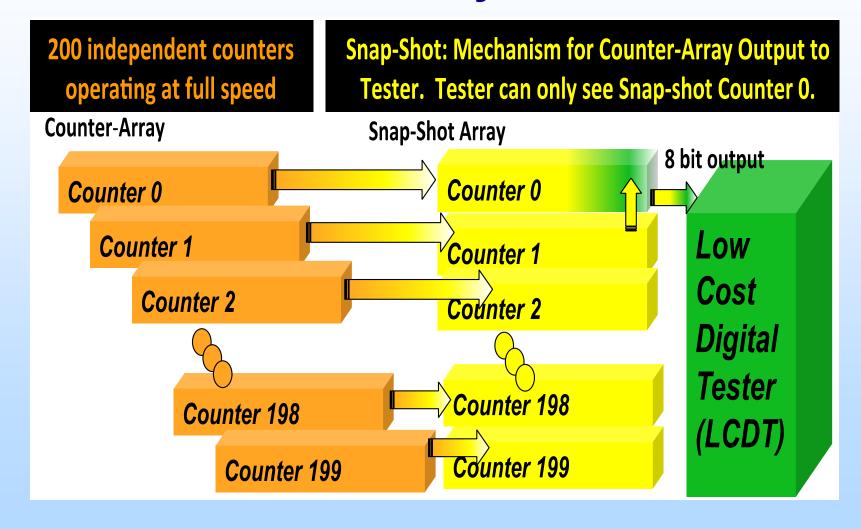

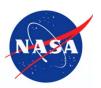

# NASA Electronics Parts and Packaging Testing of the Kintex-7 FPGA: Counter Arrays

#### **SEU Cross-Section Data: (NEPP)**

### Currently, What Are The Biggest Challenges Regarding Mitigation Insertion?

- Tool availability... Synopsys is now available.

- User's are not selecting the correct mitigation scheme for their target FPGA.

- Logic partitioning is not being performed when needed.

| FPGA Type                                     | LTMR | DTMR  | GTMR |

|-----------------------------------------------|------|-------|------|

| Antifuse+LTMR: Microsemi RTAX or RTSX family  |      | 22222 |      |

| Commercial SRAM: Xilinx and Altera devices    |      |       |      |

| Commercial Flash:<br>Microsemi ProASIC family |      | ????? |      |

| Hardened SRAM: Xilinx V5QV                    |      | ????? |      |

Not Recommended but may be a solution for some situations

Will not be a good solution

### **User versus Embedded Mitigation**

- A subset of user inserted mitigation strategies have been presented.

- None of the strategies are 100% fail-safe.

- Depending on the project requirements, and the target device's SEU susceptibility, the most efficient mitigation strategy should be selected.

- In most cases, devices with embedded mitigation do not require additional (user inserted) mitigation.

#### **Fail-Safe State Machines**

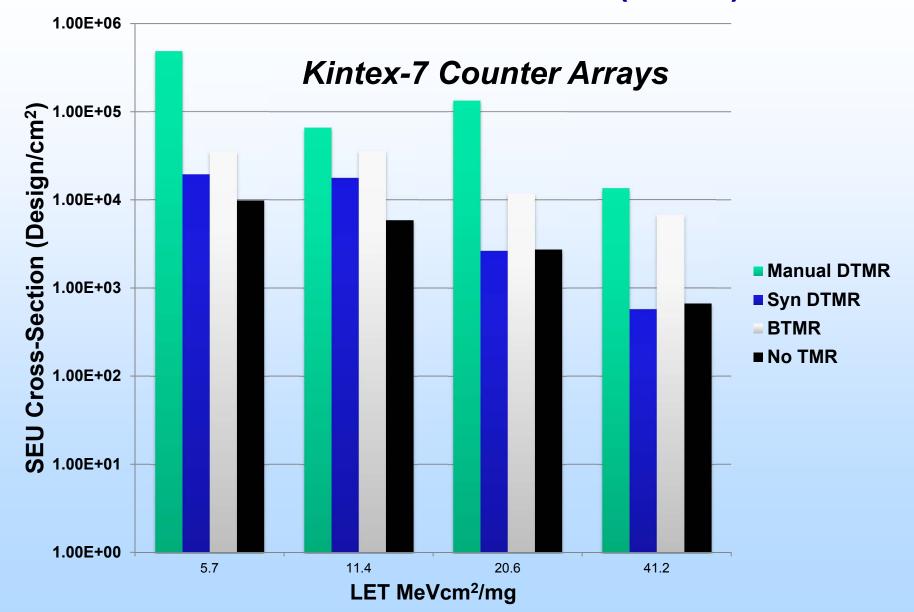

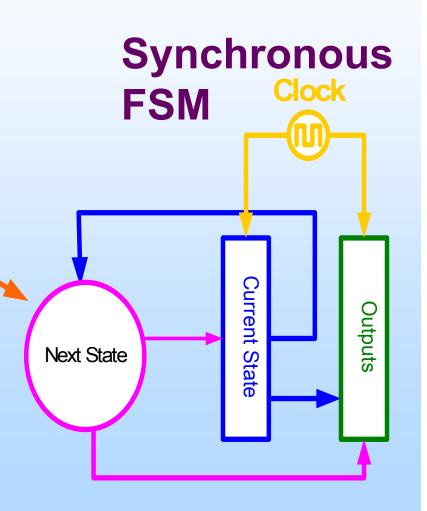

### Synchronous FSMs and SEUs

- A synchronous FSM is designed to deterministically transition through a pattern of defined states

- A synchronous FSM utilizes

DFFs to hold its current

state, transitions to a next

state controlled by a clock

edge and combinatorial

logic, and only accepts

inputs that have been

synchronized to the same

clock

- FSM SEUs can occur from:

- Caught data-path SETs

- DFF SEUs

- Clock/Reset SETs

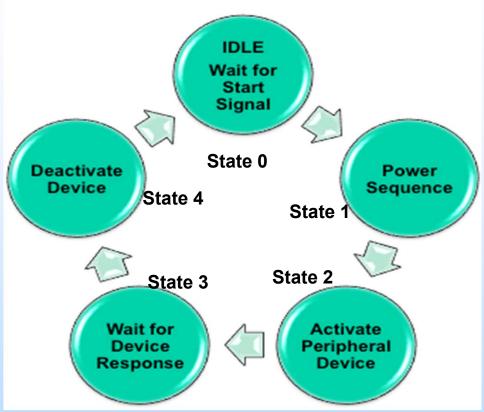

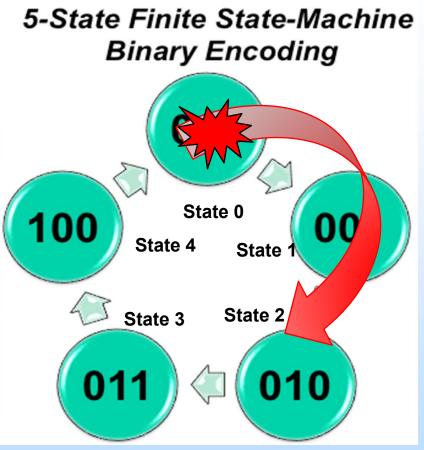

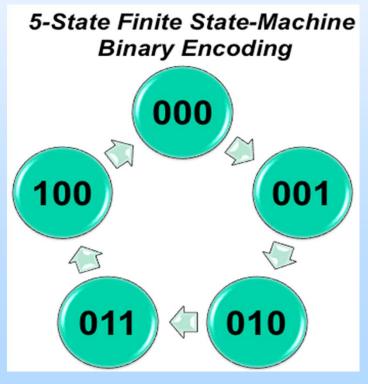

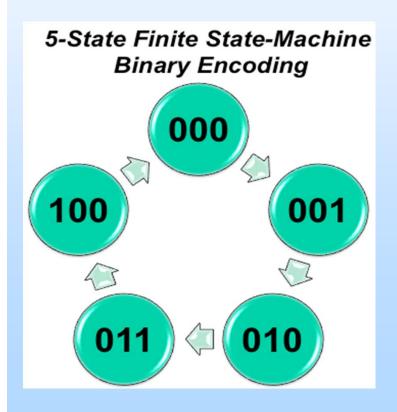

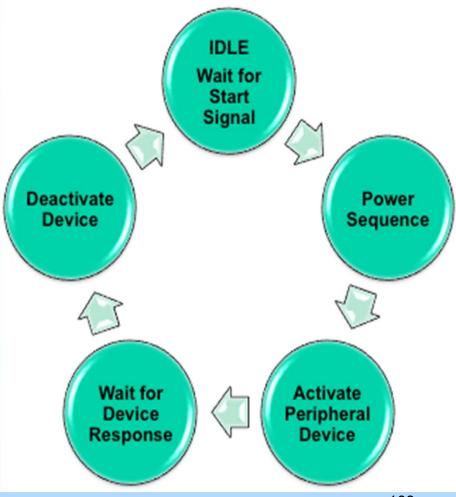

#### 5-State FSM Binary Encoding Example

#### 5-State Finite State-Machine

Example of an FSM used to control a 5-State peripheral device encode

5-State FSM with each state encoded as binary numbers.

An SEU can change current state and cause a catastrophic event

### How Do We Implement Fail-Safe FSMs?

- Question: A designer states that all FSMs have been implemented as "safe", what do you expect?

- Correction? Detection? Masking?

- What does correction mean?

- All mitigation shall be defined unambiguously by the requirements and by the designer.

#### **Safe State Machines**

As currently defined by design tools and by some designers, the term "safe" state machine is a misnomer.

Auto transitioning ("safe state-machine") is a reaction to a small subset of incorrect transitions (unmapped states).

They do not correct or mask (protect) against incorrect

transitioning.

What happens if an SEU causes a transition from "001" to "101"?

| State | Mapped or Unmapped |

|-------|--------------------|

| 000   | Yes                |

| 001   | Yes                |

| 010   | Yes                |

| 011   | Yes                |

| 100   | Yes                |

| 101   | No                 |

| 110   | No                 |

| 111   | No                 |

# Safe State Machines: What happens if an SEU causes a transition from "001" to "101"?

- As currently implemented, a "safe" state machine will automatically transition to a reset (or "safe" state).

- Problem: this could be detrimental to your system

| State | Mapped or Unmapped |

|-------|--------------------|

| 000   | Yes                |

| 001   | Yes                |

| 010   | Yes                |

| 011   | Yes                |

| 100   | Yes                |

| 101   | No                 |

| 110   | No                 |

| 111   | No                 |

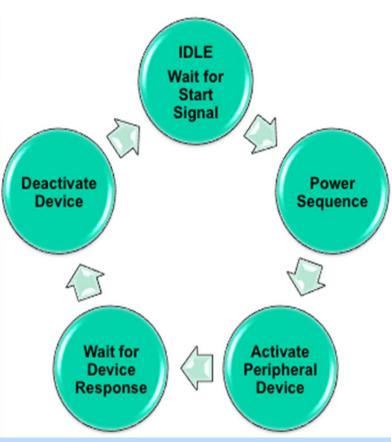

### Problems with Current "Safe" FSM Definition

NASA

- Sounds more safe than what it really is.

- Does not do anything for incorrect transitions into mapped states.

- Does not correct the state:

- Something that is supposed to be on will abruptly shut off.

- Other FSMs or control logic can become unsynchronized with the bad FSM; with or without the automated jump to a "safe" state.

#### 5-State Finite State-Machine

### Can Auto-transitioning Work for Your Mission?

NASA

- Auto-transitioning can work if incorrect sequencing of your FSM will not cause system failure; e.g. mathematical logic control.

- Auto-transitioning can be acceptable if it is used in conjunction with a detection flag.

The detection flag must propagate to all necessary logic.

- But remember, there is no protection or detection with autotransitioning when incorrectly transitioning to a mapped state.

Auto-transitioning + detection is available with computer aided design (CAD) tools.

5-State Finite State-Machine

### **Implementing Corrective Logic for FSMs**

- FPGAs with hardened configuration:

- LTMR: Triplicate each DFF and use a majority voter.

- The triplication + voter is treated as one DFF

- Encoding doesn't change

- Resultant FSM has 3 times the number of DFFs than the original encoding scheme.

- Combinatorial logic (not including the voters) does not change

- Hamming Code-3: requires a new encoding scheme.

- FPGAs with commercial SRAM configuration: DTMR is suggested.

There are computer aided design tools (CAD) that can assist in adding all of the above mitigation strategies.

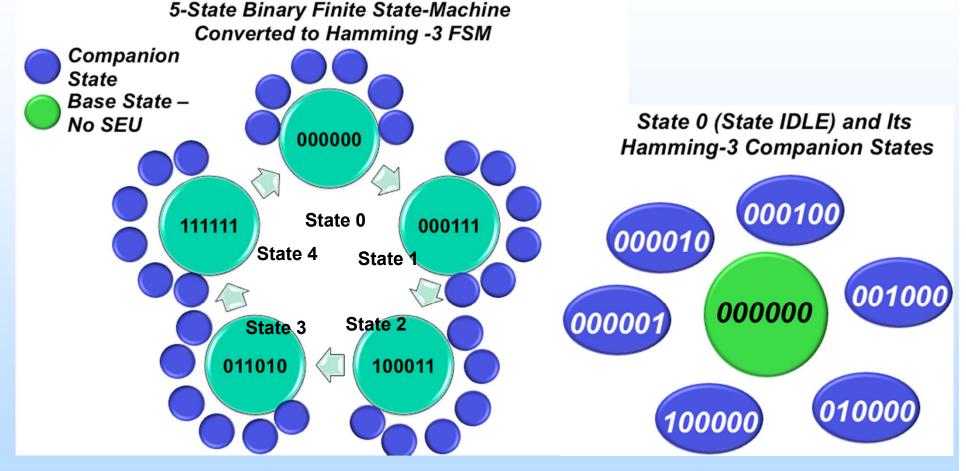

# FSM Fault Tolerance: 5-State Conversion to a Hamming Code-3 FSM

Hamming Code-3 FSM Diagram for a 5 Base-State FSM: Would need 5\*7=35 FSM states to be represented... 6 DFFs A closer look at a base-state (state 0) and its companion-states

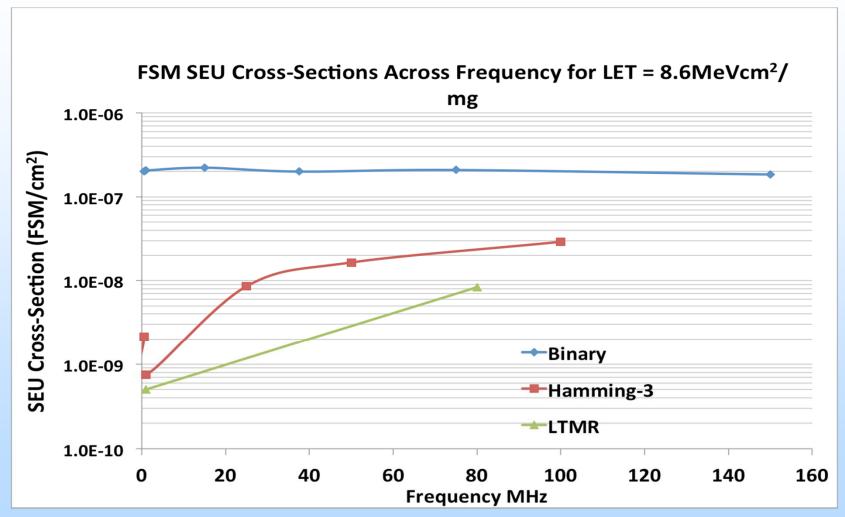

### **ProASIC3 Heavy-Ion FSM SEU Testing**

SEU cross-sections per FSM.

Scale is Log-Linear

### **Some Thoughts**

# Concerns and Challenges of Today and Tomorrow for Mitigation Insertion

- User insertion of mitigation strategies in most FPGA devices has proven to be a challenging task because of reliability, performance, area, and power constraints.

- Difficult to synchronize across triplicated systems,

- Mitigation insertion slows down the system.

- Can't fit a triplicated version of a design into one device.

- Power and thermal hot-spots are increased.

- The newer devices have a significant increase in gate count and lower power. This helps to accommodate for area and power constraints while triplicating a design. However, this increases the challenge of module synchronization.

- Embedded mitigation has helped in the design process. However, it is proving to be an ever-increasing challenge for manufacturers.

- We (users) want embedded systems: cheaper, faster, and less power hungry.

- However, heritage has proven that for critical applications, embedded systems have provided excellent performance and reliability.

### **Summary**

- For critical applications, mitigation may be required.

- Determine the correct mitigation scheme for your mission while incorporating given requirements:

- Understand the susceptibility of the target FPGA and how it responds to other devices.

- Investigate if the selected mitigation strategy is compatible to the target FPGA.

- Calculate the reliability of the mitigation strategy to determine if the final system will satisfy requirements.

- Ask the right questions regarding functional expectation, mitigation, requirement satisfaction, and verification of expectations.

- Although it is desirable from a user's perspective to have embedded mitigation, cost seems to be driving the market towards unmitigated commercial FPGA devices. Hence, it will be necessary for user's to familiarize themselves with optimal mitigation insertion and usage.